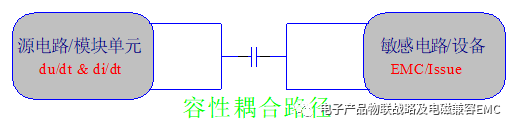

2.容性耦合路徑問題

注意電路中任意相近的兩根電流導線都會存在分布電容耦合:PCB走線 及 連接線等等;

我通過下面的原理分析框圖來進行詳細的說明;后面再給出我碰到的實際案例進行參考-分析電子產品&設備中的感性耦合與容性耦合問題;

上面的原理路徑示意框圖設計到的信息非常廣,可以延伸到不同的電源拓撲結構;涉及到系統的傳導理論,輻射理論;如果上面的電路你就當做是標準的PFC大功率應用電路;這時候你就會考慮30MHZ-300MHZ的騷擾功率的問題!如果電路結構前級輸入是低壓的交流輸入(例如12VAC)這個電路可以是標準的升壓(BOOST)電路結構;改變一下電感,開關MOS及輸出二極管的位置;這個電路就可以變成高壓或中低壓的降壓(BUCK)電路;也就是說這類電路的應用在EMI的問題表現及處理上都可使用同樣的等效結構;處理EMI的問題就非常類同了。

A.在上面的電路結構中電感回路及輸出回路比較優化,并且和交流輸入有足夠的距離時;如果有EMI的問題請參考《開關電源:EMC的分析與設計》快速設計理論方案!

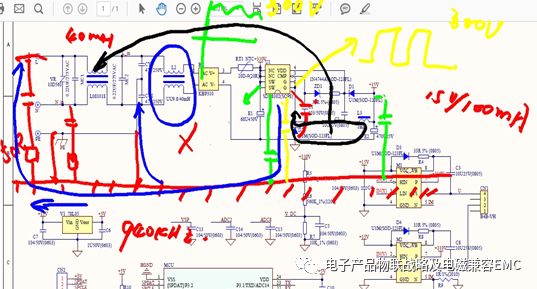

B.我在進行企業內訓時就出現實際的特別案例;EMI傳導設計-中高頻部分優化我們共模濾波器沒有明顯的效果;分析框圖結構如下:

該電路結構是典型的交流220VAC整流濾波后進行BUCK電路的高壓降壓電路設計,輸出15V/0.1A 典型系統供電電路;EMI電路的濾波電路使用2級濾波器結構;我進行上述的EMI的路徑分析這個2級濾波器完全足夠解決150KHZ-10MHZ的傳導干擾;進行分析如下:

1.檢查PCB設計電路中的BUCK電感距離輸入EMI濾波器較近;BUCK電路的高壓電容的環路及續流二極管的環路面積均較大,且走線靠近輸入濾波器走線!

由此分析如上圖中黑線環路及路徑造成了>940KHZ到幾MHZ的EMI頻段多點超標問題;(感性耦合-工字型電感 & 關鍵走線-容性耦合)

2.采用最簡單的方式來判斷問題;使用一個磁環將交流輸入電源線繞3圈及以上;EMI超標點立刻消失并且通過EMI測試!

3.通過上面的磁環驗證很明顯我們找到解決問題的方法:去掉1級共模電感;使用一個雙線并繞的共模電感(1-5mH均可)放置在電路板的電源線入口進行測試;整個EMI測試數據均達到10dB以上的裕量!